OCTOBER 2022 MAGAZINE |Connect007 UFIDI BEYOND!

#### 1.00%Books

## Distinctly different.

Our books are written by recognized industry experts. At around 8,000 words, they are unique in that they are able to be incredibly focused on a specific slice of technology.

"I-007ebooks are like water in the desert ...it's up to you to drink it in order to survive!"

Stephen V. Chavez PCEA Chairman, MIT, CID+

#### **VISIT OUR LIBRARY**

### The heat is on!

## THE PRINTED CIRCUIT DESIGNER'S GUIDE TO....

### Thermal Management with Insulated Metal Substrates

Didier Mauve and Robert Art Ventec International Group

# DESIGNOUT

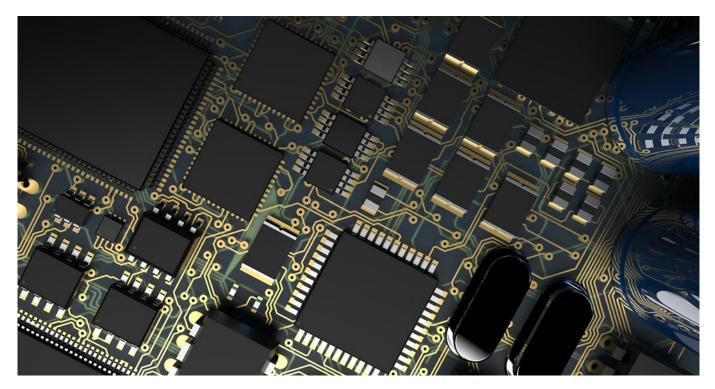

### To UHDI and Beyond!

It is tough to get much smaller than ultra HDI. This is a whole new level of miniaturization for most PCB designers and fabricators. UHDI folks speak in terms of microns, not mils. And everything changes when you start working with 15-micron lines and spaces. For this issue, we asked some of the top UHDI experts to share their knowledge about designing and fabricating these tiny features. Join us as we journey to UHDI and beyond!

**FEATURE INTERVIEWS** 10 **Ultra HDI Primer** with Herb Snogren

- The Learning Curve for Ultra HDI 32 Q&A with Tara Dunn

- Forming Standards for Ultra HDI 48 Q&A with Jan Pedersen

**FEATURE ARTICLE** A Designer's 20 **Point of View** by Cherie Litson

by Vern Solberg Scaling PCB Design to the Power of 10 64

Let's Get Small 8 by Andy Shaughnessy

**Ultra High-Density** 42 **Circuit Board Design**

by Kelly Dack

## ANNOUNCING... ALL FLEX SOLUTIONS

THE MERGER OF PRINTED CIRCUITS, LLC AND ALL FLEX, INC.

# ALL YOUR FLEXIBLE SOLUTIONS ALL IN ONE PLACE

Call us today for your flexible application!

507-663-7162 AllFlexInc.com

Flexible circuit solutions

Rigid flex solutions

**CatheterFlex™ solutions**

Flexible heater solutions

And assembly solutions too!

# DESIGNO07

#### **SHORTS**

- Discovery of New Nanowire Assembly Process Could Enable More Powerful Computer Chips

- 39 A World First: Self-calibrated Photonic IC: New Interchange for Optical Data Superhighways

- Infographic: Anatomy of Ultra HDI

- At the Water's Edge: Self-assembling 2D Materials at a Liquid-Liquid Interface

- Researchers Develop Novel Spectrum

Sensing Technique for 6G-oriented

Intelligent IoT Communications

#### **DEPARTMENTS**

- **97** Career Opportunities

- 108 Educational Resource Center

- 109 Advertiser Index & Masthead

#### **HIGHLIGHTS**

- 40 MilAero007

- 62 PCB007

- 80 Flex007

- 94 Top Ten Editor's Picks

#### COLUMNS

**26** Routing Strategies to Minimize Radiation by Barry Olney

- 36 The ABCs of Clean Schematics by Matt Stevenson

- 52 Thermal Management Isn't Getting Easier by John Coonrod

- **56** Noise Mitigation in Power Planes by Istvan Novak

- **70** Avoiding Conformal Coating Pitfalls by Saskia Hogan

- 74 Unblocking Innovation With a Component Digital Thread by Matt Walsh

#### **FOCUS ON FLEX**

Market and Tech Convergence:

Electrically Conductive Inks

by Stan Farnsworth

- 86 The Chameleon of Interconnection Technologies by Joe Fjelstad

- 88 The Printed Electronics Roundtable, Part 3 with John Lee, Kevin Miller, Tom Bianchi, Mike Wagner, and John Voultos

# A comprehensive, digitally integrated electronic design solution for enterprises of all sizes.

- Digitally-connected ECAD to the rest of the enterprise

- Cross-domain and cross-discipline collaboration

- Digitally-managed workflows, processes and resources

As the most lightweight, easy-to-implement electronics design solution for enterprises, Altium NEXUS makes the last mile of digital transformation not only possible - but easy.

### Let's Get Small

#### The Shaughnessy Report

by Andy Shaughnessy, I-CONNECT007

Comedian Steve Martin could have been talking about this issue of *Design007 Magazine* when he released his album "Let's Get Small" in 1977—or maybe not. Well, as Steve would say, excuuses me! (You may have to explain that reference to any young people in your company.)

But it is tough to get much smaller than ultra HDI. This is a whole new level of miniaturization for most PCB designers and fabricators. UHDI folks speak in terms of microns, not mils. Everything changes when you start working with 15-micron lines and spaces.

The IPC D-33AP Task Group is working hard at updating standards for UHDI because standards can barely keep up with UHDI processing. Cleanliness becomes all-important at that level, as a speck of dust can wreak havoc

on UHDI circuitry. We're talking about nearcleanroom quality.

When we started planning this issue, we quickly discovered that there aren't that many UHDI experts in North America; the overwhelming majority of UHDI technologists and facilities are in Asia. As a designer half-jokingly told me recently, "Most of the world's experts in UHDI speak Mandarin." (I only know about 10 words in Mandarin, and half of those are slang, so that could be a problem.)

The DoD has begun to recognize that the United States is behind the rest of the world in critical electronics manufacturing, and UHDI is a perfect example. But it's no easy feat for a fabricator to jump into UHDI; a direct imaging machine alone runs close to \$1 million.

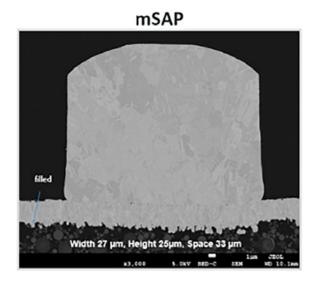

Even as the use of UHDI continues to grow with processes such as A-SAP and mSAP, there's a dearth of information available in English. Very few instructors in our industry teach UHDI design or fabrication curriculum, and there are not many UHDI resources online or elsewhere. We realized this was a great chance for Design007 Magazine to help fill that void by focusing on UHDI processes.

So, we asked some of the top UHDI experts to share their knowledge about designing and fabricating these tiny features. In this issue, we cover the challenges and opportunities in UHDI design, and the level of commitment required to become one of these top-level designers. Our goal is that you understand the critical points in the UHDI fabrication process to advance your capabilities of UHDI design.

In our conversation with Royal Circuits' UHDI expert Herb Snogren, he explains exactly what constitutes ultra HDI, where the current cutting edge lies, and the hurdles facing anyone who wants to design or manufacture boards at the 20-micron level or below. Instructor Cherie Litson breaks down the semi-additive manufacturing process and shares some of her tips and tricks for designing A-SAP and mSAP circuits. Columnist Tara Dunn explains how to speed up the "learning curve" for UHDI circuits, and she answers common questions from new UHDI technologists.

Columnist Vern Solberg discusses how to conduct an interconnect capacity analysis to determine whether a design should utilize HDI or UHDI features. Jan Pedersen of NCAB, co-chair of the IPC D-33-AP Subcommittee, details their efforts to form UHDI standards. Kelly Dack then describes how he suddenly found himself working on designs with 15-micron lines and offers some advice for working on these tiny features.

We bring you columns from Barry Olney, Matt Stevenson, John Coonrod, Istvan Novak, Saskia Hogan, Matt Walsh, and Joe Fjelstad. In our flex space, we have an article by Stan Farnsworth and the concluding installment of our printed electronics roundtable with Kevin Miller, Mike Wagner, John Voultos, and Tom Bianchi.

There's a real need for information about UHDI. As you move forward into the world of microns, I hope you will consider this month's Design007 Magazine as a reference. One final note, if you haven't already, be sure to follow us on LinkedIn and Twitter. There you'll find updates and links to many of our most popular features. Let's have a conversation online, and get small! DESIGNO07

Andy Shaughnessy is managing editor of Design007 Magazine. He has been covering PCB design for 23 years. To read past columns, click here.

### **Ultra HDI Primer**

Feature Interview by the I-Connect007 Editorial Team

We recently spoke with Herb Snogren, an industry veteran and consultant with Summit Interconnect tasked with leading the company's ultra HDI efforts. Herb is co-chair of the IPC ultra HDI subcommittee, IPC D-33-AP. In this interview, Herb discusses the current state of UHDI, how designers and fabricators can get started working in this new frontier, and why the U.S. must invest in UHDI technology now to counteract Asia's near dominance of the UHDI segment, which has left some of our critical industries vulnerable to supply chain disruptions.

**Andy Shaughnessy:** Herb, almost everyone I talk to about this topic asks me, "What is the definition of ultra HDI?" What's the manufacturable limit?

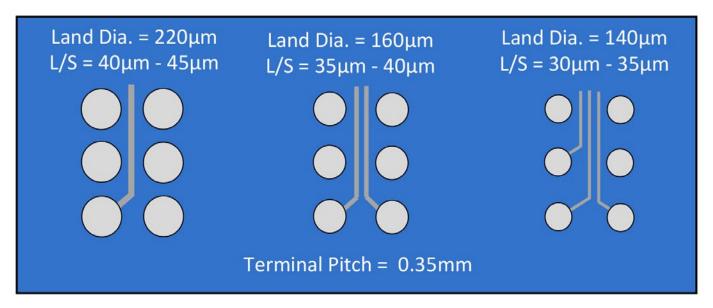

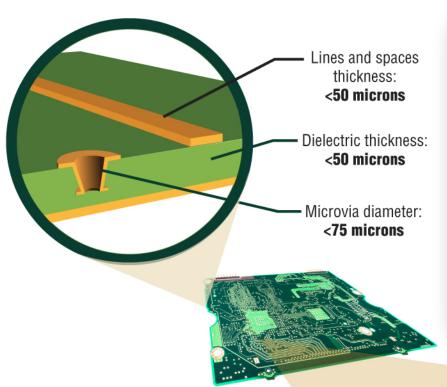

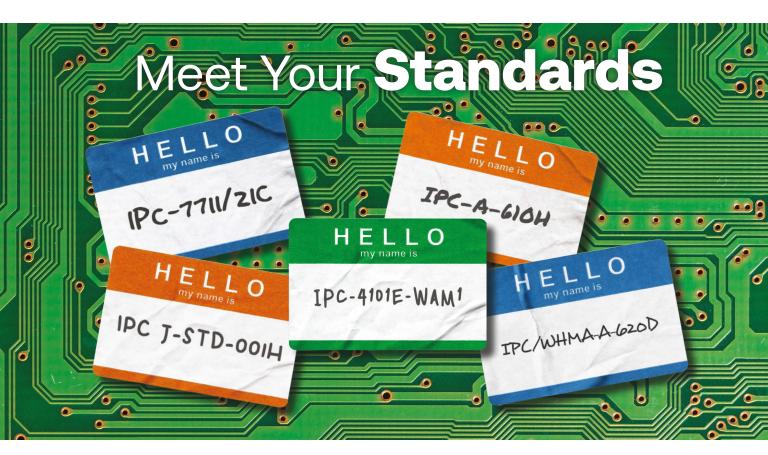

Herb Snogren: We've developed an IPC sub-committee, IPC D-33-AP. Jan Pedersen of NCAB Group is my co-chair, and we've defined ultra HDI as printed circuit boards that have line widths and spaces below 50 microns, and microvias at 75 microns and below in diameter. We came up with that delineation because of IPC-2226, which lists product attributes with producibility levels A, B, and C. Level C is the lowest producibility level and that stops at 50-micron lines and spaces.

**Shaughnessy:** Tell us about the committee's efforts.

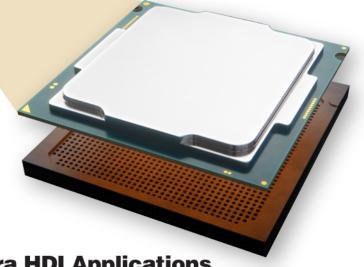

**Snogren:** What's important to understand is that circuit boards are following the path of packaging substrates. We now have the term

# A Total PCB Solution from a Single Manufacturing Partner

With an experienced staff and eight high-tech facilities, Summit Interconnect provides customer-focused services to move your PCBs from prototype through production.

As the largest, privately held PCB manufacturer in North America, we provide the best customer experience and a complete portfolio of high-mix, low-volume products including high-density rigid, flex and rigid-flex, RF/microwave, and semiconductor/ATE PCBs.

Quote your project today!

Herb Snogren

SLP (substrate-like PCB) because printed circuit boards, at least in Asia for small form-factor products, are being produced with manufacturing techniques similar to IC substrates. IC substrates now have line widths and spaces down to 6 and 8 microns, and that's where we're going. When you look at some of the Apple and Samsung products, they're in the 20- to 25-micron line and space range in high volumes.

**Shaughnessy:** For years, we've been hearing that the convergence of IC and PCB processes was on the horizon. It seems like we're finally there now.

**Snogren:** We are. Historically, IC substrates were made with semi-additive or modified semi-additive processing, and now printed circuit boards are being made with semi-additive and modified semi-additive processing. It is really happening.

**Shaughnessy:** Is Asia the center of ultra HDI?

**Snogren:** Yes. It really started with Apple working with their suppliers in Asia to get their line widths and spaces down. They did it in a big

way, but because of that, other companies are taking advantage of the capability that's been established. There are companies in other parts of the world that can do that. There may be one or two in Israel and Europe, but more than 95% of the volume is being done in Asia, with most of it in China.

**Shaughnessy:** What segments are driving the development of ultra HDI?

**Snogren:** It's anything that has a small form factor. It started with the cellphone, just trying to pack more capability into a small space. You see it in medical devices that need to be small, such as in-ear devices or hearing aids. We need to do implantable devices that must be small and innocuous. With heterogeneous integration and cramming more transistors into a square inch through heterogeneous packaging, there are more I/Os on the device. The I/O density increases, so your pitch decreases, and that's driving this as well.

**Shaughnessy:** Are design engineers from the PCB side studying IC laminate design processes, and vice versa?

**Snogren:** Product designers need to understand there is a manufacturing process capable of producing these finer features, and they can employ those in their products to reduce the size of the product or reduce layer count. The problem is you can't get it in the United States, so if they design it, they don't have a place to buy it here. You must go to Asia. Right now, companies are trying to develop it. Averatek has some licensees who can do this. Winonics (Additive Circuits Technologies) has a similar technology it is developing. But I don't know if anyone is doing anything in a meaningful way or volume. Certainly not in any kind of volume at this point.

**Shaughnessy:** UHDI seems to be uncharted territory. What's the biggest hurdle for fabricators who want to get involved? What will they need to learn and upgrade?

**Snogren:** On the equipment side, you must invest in direct imaging equipment that has 20-, 25-micron feature size capabilities or less. You find resists that are compatible with your imaging system. Then there's AOI equipment. You need specialized plating equipment for doing simultaneous pattern plate and microvia filling, and equipment for handling thin foil and ultra-thin foil, 1- to 3-micron foils, and differential etching equipment. If they want to go fully into semi-additive processing, they should look into something like Averatek or eSurface to get electroless copper to stick to a wide variety of laminates.

**Shaughnessy:** Because this is all build-up at this point, right? You can't do subtractive at this level.

**Snogren:** It's difficult. Asian fabricators were doing subtractive down to 30- to 40-micron lines and spaces. Once they hit that point, most of them started using modified semi-additive processes. One big aspect is cleanliness. I don't know that any of us in the U.S. understand the cleanliness aspect of it, and how clean our processes must be. Once you start running in volume, those small particulates that don't bother you when you're at 3-mil line and space suddenly become a big percentage of a 20-micron line and space. We may have to deal with much different environmental issues in our factories with clean air, water, and processing tanks, ultra-filtration, special handling. It's going to be different.

**Nolan Johnson:** It seems that we're down to the dimensions that triggered cleanroom environments in the IC world 20 or 30 years ago, and that was very successful. We will be looking at that for our fabrication facilities in those dimensions as well, which will raise the cost of a UHDI facility.

**Snogren:** Yes, it will be difficult to justify having this cleanroom environment and ultra-filtered processes and air just to build standard 4-layer or 6-layer 4-mil line and space products. That's why some Asian factories doing these types of products are specialized. All they do is build these HDI and ultra HDI products.

**Shaughnessy:** It seems like a big opportunity here for our fabricators.

**Snogren:** It's a chicken or the egg scenario. You must develop the capability and hope people will buy it. But if you don't develop the capability, they won't even design those features because they can't get it. It's a tough investment decision to make for companies in North America. But I believe if you have the capability and demonstrate it, people will begin to design products that take advantage of that capability.

It's a chicken or the egg scenario. You must develop the capability and hope people will buy it.

Shaughnessy: Will UHDI change the PCB designer's job?

**Snogren:** The HDI design standards in IPC-2226 don't really address some of the requirements for feature sizes, alignments, and spaces below 50 microns very well. That's something that our D-33-AP committee is trying to address. How do the design standards need to change or how do we need to adapt them for ultra HDI features?

Here are some things that we've already identified: The plating thickness requirements, annular rings, and dielectric thicknesses are different. We may not even use foil if we go to semi-additive, and many of the design standards

don't address that. Of course, 6012 needs to be modified as well to allow for thinner copper conductors because they're not doing 1 mil or 1.2 mils of plating on line widths that are 20 microns and below. They're typically in the 12- to 18-micron thickness range, which doesn't meet 6012. Solder mask thicknesses may need to decrease when you have devices with 0.2-millimeter BGA pitches; you can't have thick solder mask or you get a standoff.

**Shaughnessy:** What about EDA tools? Can they go down to the 20-micron level?

**Snogren:** Yes. That's not a problem as far as EDA tools go, because a 25-micron line is just another D-code in the system. Some of the design rule criteria would be different, certainly, such as the annular rings. Some of the requirements that you would have on the drawing with conductor thickness or plating thicknesses would be different.

**Shaughnessy:** It seems like, as far as signal integrity, there would be a lot of advantages, but still quite a few hurdles as well.

**Snogren:** Yes. UHDI can be beneficial in one way: You can certainly get a higher precision line width and spacing when you're doing

semi-additive processes because your etch loss is virtually nothing. You can be very precise, but you're dealing with very small features and any minor imperfection will cause an issue that you wouldn't see on a 3-mil line and space job.

**Shaughnessy:** It seems like at this level you would want to simulate and run analysis every time?

**Snogren:** Yes, and you need to do that in conjunction with the fabricator because there are so many different techniques now for manufacturing a given feature. You can do it with subtractive, semi-additive, or modified semiadditive. They will all give you a slightly different result in maybe conductor thickness or tolerance. You must work in conjunction with the fabricator, understand their process, what the result will be, and design around their process. It's no longer just designing it, throwing it over the fence, then seeing who will snag it and try to build it. There must be more cooperation between the designer and the fabricator.

**Shaughnessy:** I mean, you're not going to start off an ultra HDI project without already having your fabricator selected. You've said that some vias are the thickness of a human hair?

**Snogren:** That's right. They're getting down below 3 mils in diameter. You're looking at 25to 50-micron diameter microvias.

**Shaughnessy:** That's really intriguing. What does the typical UHDI process look like?

**Snogren:** It will be a buildup technology, where you start with a core and sequentially build layers on both sides as you go, using microvias as an interconnect between the layers. In some ways that's easy because registration is so simple. Each layer automatically registers to the layer below it, and you really don't have the kind of mismatch in registration that we have with regular multilayer boards and blind

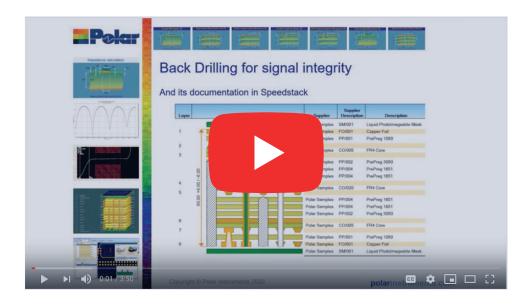

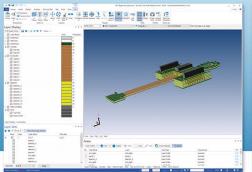

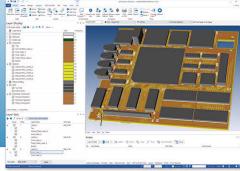

Integrated Tools to Process PCB Designs

**Document**

Quickly and easily specify the PCBs form, fit and function.

Use manufacturing data to generate a 3D facsimile of the finished product.

Ensure that manufacturing data is accurate for PCB construciton.

Minimize costs in both PCB fabrication and assembly through maxiumum panel usage.

**Panelize**

**CAM350**

Verify and Optimize PCB Designs for Successful Manufacturing

Drive Fabrication, Assembly & Inspection

DownStream Technologies, offers an integrated manufacturing data preparation solution for PCB post processing including manufacturing data visualization, stack-up definition, PCB panel visualization and support for 3D PCB documentation. This environment allows PCB designers and engineers to visualize, verify and document a printed circuit board before manufacturing.

800-535-3226 downstreamtech.com

©2019 DownStream Technologies, Inc. All rights reserved.

and buried vias. It's a sequential process. If you have five lam cycles sequentially, and you screw up the last one, you just burned up two to four weeks of work and you have to start over.

**Shaughnessy:** Now, much of this wouldn't have been possible even 10 to 15 years ago because these enabling technologies didn't exist, right?

**Snogren:** Direct imaging is a big one. That has helped with registration and feature size capabilities. When we were using film in the past, we had registration issues because the film moved, and we had to register it manually. It expanded and contracted with temperature and humidity. We had to pin it and the pinning wasn't always perfect.

Now we can have much smaller annular rings, much smaller feature sizes. With film, typically we had a really hard time getting down to 2-mil lines and spaces consistently when we were using a phototool. Not that it can't be done because they use phototools for ICs, but they're tiny and they use stepper cameras. They're not doing panels on a single sheet of film. Direct imaging is probably the biggest example. Anybody can buy a direct imaging system that can go down to 12 microns and maybe even less if you want to spend the money. If you get the

right resist, you can resolve 20-micron lines and spaces fairly easily. That was unheard of 10 years ago. You couldn't even think about it.

**Shaughnessy:** Where are the bottlenecks in this whole process? Where do we need to innovate?

**Snogren:** It's just adopting the thin foils. Designers need to understand what the manufacturing process is like so they can design around it, whether it be using thin foils or semi-additive process with electroless copper. It's about understanding what the copper thicknesses will be, what the feature size capabilities are. For the fabricator, it's about getting the systems in place: the direct imaging system, AOI, electrical test, differential etch, the proper via fill and laser drill capabilities. HDI manufacturers already have these, so it's just a matter of adapting them to a slightly different process flow and adding a few other processes.

**Shaughnessy:** I keep hearing about the Asian companies doing UHDI well and for fairly cheap. What do we need to learn from them?

**Snogren:** They've already adopted modified semi-additive processing and semi-additive processing. With the modified semi-additive processing, which gets you down to 20- or 25-micron lines and spaces relatively comfortably, we must copy what they're doing. Remember, when they do this in Asia, it's in a factory that was designed to do nothing but that. They're not building a wide variety of products; they're only doing ultra HDI.

**Shaughnessy:** Those are all greenfield facilities.

**Snogren:** It's what they do all day, so it's a fairly standardized well-controlled process where they build things that are within a narrow design feature range.

**Shaughnessy:** What percentage of ultra HDI now is mSAP or A-SAP?

**Snogren:** When you look at printed circuit boards on the high-end cellphones, watches, and things like that, almost all of that is mSAP. The semi-additive process really is being used more on the packaging substrates, and they're using either electroless copper or vacuum-deposited copper on those products. I don't know that many circuit board manufacturers are trying to use semi-additive processing in volume anyway. But with Averatek, the licensed companies are starting to use that. It's certainly a viable way to approach it.

**Shaughnessy:** You mentioned that our process,

our technologies, should learn to be more like the semiconductor industry, that we should learn from them. What are some things that we should take away from the way semiconductor manufacturers have been doing it?

**Snogren:** When they design a factory, it's around a capability. They deal with a process node and technology node, and if you're a semiconductor designer, you design into that node, you design into that factory. They don't just accept

any design. They give you the design criteria in a file and you must follow that criterion. If you don't, they don't build it.

**Shaughnessy:** We had a magazine focused on design rules several months ago. With ultra HDI, will we need to have some uniform design rules and constraints?

**Snogren:** We need some general ones, and my IPC committee is working to develop those guidelines. We are developing a general guideline so designers know when they need to

diverge from IPC-222x and IPC 60xx standards. We're trying to make it process agnostic as much as possible. We want it to be more general, suggesting that the designers talk to and work with their suppliers more closely on the design because they may use multiple techniques to fabricate the job. We haven't even talked about fully additive with inkjet printing conductors.

**Johnson:** When we start talking about UHDI, do you see that as the tipping point where cleanroom technology needs to happen? Is UHDI where we move to just greenfield facilities?

**Snogren:** For volume, yes. If you want to do volume and repetition, and do things with good yields, there's no doubt in my mind that's the case. For small companies in the U.S. that want to offer that as a capability, I don't really know where we start to run into the hurdles. I've been running some testing on 25-micron lines and spaces here and I haven't gotten to the point where it's become an issue, but we haven't really done a lot of volume. A dedicated

facility is the way I would go for high volume. For an existing HDI factory, I believe one can produce small quantities of UHDI product with a decent cleanroom for the imaging processes and good filtration in electroless copper and electrolytic copper plating.

**Johnson:** Now it starts to feel like integrated circuits where, as you were saying, you build the factory around a particular technology. It feels like we're on the cusp here of having the cutting-edge printed circuit board fabrication philosophy start to look like IC.

**Snogren:** Yes. And when Apple decided it needed UHDI, the company didn't just throw designs over the fence and get somebody to build it. They went to companies like AT&S and Multek, and said, "Here's where we need to go. Here's our roadmap. Start developing capabilities to get there." They started doing that in factories that were already pretty specific to a certain capability anyway. I have friends who worked at a Multek HDI factory in Zhuhai. They said Apple and Samsung were migrating from 50-micron line and space to 40 and 35, then saying, "We've hit the wall in this factory. We're having to build a factory somewhere else that's going to do mSAP."

**Johnson:** Well, that's a fundamental shift for thinking in North America, for sure, and Europe as well.

**Snogren:** You can't be all things to all people. That's the thing. Multek is a good example. On their campus in Zhuhai, they have an HDI factory, a flex factory, a daughter board factory, and a back panel factory, and they're very segregated for a very specific type of printed circuit board.

#### You can't be all things to all people. That's the thing.

**Shaughnessy:** Are there any good resources to learn more about ultra HDI, maybe in the form of websites, books, or instructors?

**Snogren:** Yes, there are a few resources, but not many. I learned about semi-additive processing when I first started.

**Shaughnessy:** How did you get into ultra HDI? Your father, Richard, wrote for me years ago.

**Snogren:** My father owned a circuit board factory, Reliable Circuits in Clearwater, Florida, when I was in high school. I worked there during college. After college, I worked at a couple of circuit board shops in Denver. Then my dad and I decided to start a shop in Colorado back in the mid-'80s, and we ran that for 16 years. I went to Coretec for a while, and then got hired as a consultant by Viasystems. I was in China for four years at the Guangzhou factory and the Zhongshan factory. I got to see another side of things. It's just ridiculously high volume.

I've been working with smaller companies recently, like Royal Circuits, which was acquired by Summit. I helped Royal Circuits develop its HDI capability several years ago. But the migration into ultra HDI really came through my work with the DoD and the PCB executive agent. I'm on the IPC-1791 committee, and we were talking about whether we should include IC substrates into IPC-1791. We found out there really aren't any industry design or quality standards for substrates. I started researching it a little bit and educated myself about IC packaging. I realized that not much happens in the U.S., certainly none of the fabrication of the substrates. This led to the creation of the IPC-D -33-AP committee to develop design and product performance standards for UHDI PCBs.

**Shaughnessy:** What does your roadmap look like for UHDI?

**Snogren:** We developed a roadmap at Royal Circuits last year. It's interesting because I came in originally about eight years ago when Royal was doing mostly 2, 4, and 6 layers. I worked with them to develop the capabilities to build HDI. I left for a while, then I approached Milan, Royal's owner, last year. I said, "Look, you're proficient now at HDI. You can do an eight- and 10-layer buildup board with five lam cycles and stacked microvias. You're good at it, but you are limited to 3-mil line and space. Let's put a roadmap together, get you down to

25-micron line and space because, if we can develop that capability, I believe we can get designers to design around that. We're not going to have a lot of competition." We put together a roadmap that we're in the process of implementing. We're not there yet, and we've got a couple pieces of equipment we need to buy, but we're moving in that direction and it's feasible.

**Shaughnessy:** This is the roadmap that you show your customers or is this internal?

**Snogren:** It's internal now. We have established the direct imaging equipment capability and the dry film capability. We have the inspection and test equipment capability. We need to upgrade our microvia filling system and purchase a differential etcher. Once we have the via filling system and the etcher, we'll be able to produce products with 25-micron lines and spaces. Whether our yields are going to be great, I don't know. But typically, these are tiny little boards so even if the defect density is a bit high, we will still have good board yields within a panel.

**Johnson:** Right. What do we tell designers?

**Snogren:** First, work with a vendor or several vendors to determine whether they can lay

out a manufacturing roadmap. The roadmap for many OEMs could say, "We're seeing finerpitch BGAs. We're going to have to use 0.3mm or 0.25-mm BGAs and we're going to need 25- and 30-micron lines and spaces. We need you all to get there because we have a whole line of products coming in the next few years that require this." Then you pick a process and say, "We're going to use ultra-thin foil. I can already buy 1.5-micron foil, so we'll start developing this capability slowly and put together the roadmap." The designer can work with the fabricator to establish the design criteria and test vehicles and put that together. The fabricator will need to buy some equipment to support that.

From a designer standpoint, if they don't want to go straight to Asia and get what they want, they need to work with a fabricator and design around the fabricator's capability or develop that capability along with the fabricator. But it's the chicken or the egg. As a fabricator, do you invest in that capability? It's going to cost you money if you don't have potential orders coming in.

Six to eight years ago when you bought an LDI machine, you were limited at maybe 2-mil lines and spaces. Then they went down to 1-mil line and space, but they were expensive. Now, if you're buying a new direct imaging system, there's no reason not to get it with 25- or 12-micron line and space capability.

You can buy an LDI machine today for not a lot more money that's capable of getting you into ultra HDI, and it's still going to support doing your 3- to 4-mil line and space jobs. That's what happened at Royal Circuits. We bought a machine, not even for that capability, and I found out, "Hey, I can do 25-micron lines and spaces on this thing." We didn't even plan for that one.

Shaughnessy: Herb, thank you for your time today. This has been very informative.

**Snogren:** Happy to help. Thank you. **DESIGNOO7**

## A Designer's Point of View

Feature Article by Cherie Litson

LITSON1 CONSULTING

HDI—high-density interconnect—designs require some different thinking on the part of the designer. One of the first things to consider is whether you need HDI, and how much. The HDI option comes into play as soon as you purchase any components with 0.5 mm pin pitch. The number of these components and other specifications of your design will determine the amount of HDI you will need. Here's a quick list of HDI options:

- Smaller vias

- Smaller traces

- Thinner dielectrics

- Tighter solder mask clearances

- Controlled paste mask construction

Each option brings choices that will affect fabrication and assembly, so a little research is needed before making these choices. I'm only going to explore the first two, as these often determine which fabrication process you want to use.

# TAKING RELIABILITY AND PERFORMANCE TO THE

**EXTREME** Our AS9100 Rev D, ISO 9001:2015 and multiple military grade certifications (MIL-PRF-31032, MIL-PRF-50884, MIL-PRC-50110) ensure that our commitment to quality is second to none! How can we serve you? **Check out our capabilities American Standard Circuits** Creative Innovations In Flex, Digital & Microwave Circuits

#### **Smaller Vias**

A variety of options are available here:

#### Blind vias with through vias

This is the optimal choice. It adds a little expense while giving you the ability to place components on both sides of the board without having to be confined by opposing pad with different nets.

#### Blind and buried vias with through vias

This option gives you the most routing control; however, it also adds the most cost.

#### Through vias only

While this can cut fabrication costs, it limits breakout, routing, via size, and component placement. Smaller vias are dependent upon the aspect ratio of the board. Keep the board thin and most fabricators can produce smaller vias, down to 6 mils (0.15 mm) if your board measures 50 mils of thickness or less, without additional costs.

Both the A-SAP and mSAP processes can be used to plate holes. Again, the aspect ratio will make a difference. How much plating do you need? Are you plugging the vias with conductive or non-conductive material?

#### **Smaller Traces**

How small you go depends on the fabrication process you select and how small the component pin pitch is.

It's important to understand the differences between A-SAP and mSAP before you commit to a process. Standard subtractive etch processes start with very thin copper foils, etch a pattern, and then add copper for the finished traces and copper features. Table 1 is a chart for starting copper thicknesses from the IPC-6012.

When using basic core material, mSAP usually starts at the quarter-ounce copper thick-

|                     | Absolute Cu Min.<br>(IPC-4562 less 10%<br>reduction) | Plus minimum<br>plating for Class 1<br>and 2 (20 µm) | Plus minimum                   | Maximum Variable Processing Allowance Reduction <sup>3</sup> | Minimum Surface Conductor<br>Thickness after Processing<br>(μm) [μin] |               |

|---------------------|------------------------------------------------------|------------------------------------------------------|--------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|---------------|

| Weight <sup>1</sup> | (μm) [μin]                                           | [787 µin] <sup>2</sup>                               | (25 μm) [984 μin] <sup>2</sup> | (µm) [µin]                                                   | Class 1 & 2                                                           | Class 3       |

| 1/8 oz.             | 4.60 [181]                                           | 24.60 [967]                                          | 29.60 [1,165]                  | 1.50 [59]                                                    | 23.1 [909]                                                            | 28.1 [1,106]  |

| 1/4 oz.             | 7.70 [303]                                           | 27.70 [1,091]                                        | 32.70 [1,287]                  | 1.50 [59]                                                    | 26.2 [1,031]                                                          | 31.2 [1,228]  |

| 3/8 oz.             | 10.80 [425]                                          | 30.80 [1,213]                                        | 35.80 [1,409]                  | 1.50 [59]                                                    | 29.3 [1,154]                                                          | 34.3 [1,350]  |

| 1/2 oz.             | 15.40 [606]                                          | 35.40 [1,394]                                        | 40.40 [1,591]                  | 2.00 [79]                                                    | 33.4 [1,315]                                                          | 38.4 [1,512]  |

| 1 oz.               | 30.90 [1,217]                                        | 50.90 [2,004]                                        | 55.90 [2,201]                  | 3.00 [118]                                                   | 47.9 [1,886]                                                          | 52.9 [2,083]  |

| 2 oz.               | 61.70 [2,429]                                        | 81.70 [3,217]                                        | 86.70 [3,413]                  | 3.00 [118]                                                   | 78.7 [3,098]                                                          | 83.7 [3,295]  |

| 3 oz.               | 92.60 [3,646]                                        | 112.60 [4,433]                                       | 117.60 [4,630]                 | 4.00 [157]                                                   | 108.6 [4,276]                                                         | 113.6 [4,472] |

| 4 oz.               | 123.50 [4,862]                                       | 143.50 [5,650]                                       | 148.50 [5,846]                 | 4.00 [157]                                                   | 139.5 [5,492]                                                         | 144.5 [5,689] |

Note 1. Starting foil weight of design requirement per procurement documentation.

Note 2. Process allowance reduction does not allow for rework processes for weights below ½ oz. For ½ oz. and above, the process allowance reduction allows for one rework process

Note 3. Reference: Min. Cu Plating Thickness

Class 1 = 20  $\mu$ m [787  $\mu$ in] Class 2 = 20  $\mu$ m [787  $\mu$ in] Class 3 = 25 µm [984 µin]

Table 1: External conductor thickness after plating, according to IPC-6012.

ness, and A-SAP starts with bare dielectric and adds 0.2 mm of thin electroless copper. Table 1 shows typical additive copper thicknesses

2. LMI™ Coat 3. Electroless Cu 1. Substrate 4. Photoresist 5. Expose 6. Develop 7. Electroplate Cu 8. Photoresist Strip 9. Flash Etch Base Cu

Figure 1: Liquid metal ink (LMI) can change your entire process flow. (Courtesy of Averatek Corporation)

after processing. These build up in a trapezoid formation depending upon the photoresist thicknesses. The A-SAP process does not build

traces in a trapezoidal fashion.

The thicker the base copper, the more of a trapezoid shape you'll have to start with. Both can start with typical foil. When they do, mSAP usually starts with a thicker copper foil and A-SAP starts with a much thinner copper base. Averatek's Steve Iketani and Mike Vinson wrote an informative article on this topic in the July 2019 issue of PCB007 Magazine<sup>1</sup>.

Optionally, both A-SAP and mSAP can use an additive process vs. a subtractive process at fabrication using LMI (liquid metal ink) for the starting copper thickness. When using LMI to apply the starting copper, as seen in Figure 1, the density at the interface with the laminate increases dramatically.

The process flow now becomes very different. So does the shape of my traces, the copper thickness and width. Figure 2 shows an example of what this looks like.

Figure 2: Examples of A-SAP and mSAP trace constructions. (Courtesy of Averatek Corporation)

Now, as a designer, I need to have some numbers. Plus, I have a lot of questions, as should you. On the following Q&A, you will find some questions that I ask at the beginning of each A-SAP or mSAP design.

**Q**: Do I need to do anything different with my output files to the fabricator to support this?

A: No. Fabricators use additive and subtractive processes all the time. You just need to know if they have the chemistry and experience working with mSAP and A-SAP processes.

**Q**: Do I need to have a special layer for SAP processes?

A: No. These processes can be constructed on outside and inside layers. Keeping them "balanced" (per good design practices) will certainly help keep costs down.

**Q**: Can I mix thicker traces with these thinner traces on the same layer?

A: Yes, but spacing is important here. It's a good idea to group these as much as possible to support the processes. Design rules are also very important.

**Q:** How will this affect my impedance values?

A: Fine traces affect impedance, but not as much as you might think. Eric Bogatin, Chaithra Suresh, Melinda Piket-May of the University of Colorado Boulder, and Haris Basit and Paul Dennig of Averatek have published a white paper<sup>2</sup> on the effects of using fine-line traces in HDI boards. They explain it much better than I can, and I trust their analysis.

Q: Do I need to teardrop all pad entries?

A: Basically, I just have to route my designs as I normally would and consider the geometry stresses of using smaller traces as they go into solderable areas. Either teardrop or increase the trace size as it goes into a pad.

Read all you can about A-SAP and mSAP, and don't look back. Companies like Averatek have experts on hand, including Haris Basit, who will be speaking at the IPC Advanced Packaging Symposium in Washington, D.C., Oct. 11–12. Knowledge is power. DESIGNOO7

#### References

- 1. "SAP Utilizing Very Uniform Ultrathin Copper," by Steve Iketani and Mike Vinson, PCB007 Magazine, August 2019.

- 2. "Utilizing Fine Line PCBs with High Density BGAs," by Eric Bogatin, et al, Signal Integrity Journal, January 2022.

Cherie Litson, MIT/CID, CID+, is the founder of Litson1 Consulting and a master instructor at EPTAC.

Digitizing the Future 数字领域,构建未来

深圳国际会展中心 (宝安)

Shenzhen World Exhibition

& Convention Center (Bao'an)

线上展会正在开放中! Virtual exhibition is live now!

www.HKPCAshow.org

Follow Us on WeChat 关注展会官方微信 获取最新资讯

Follow Us on LinkedIn 关注展会官方领英 获取最新资讯

#### 主办单位

香港线路板协会 Hong Kong Printed Circuit Association (HKPCA)

mandawong@hkpca.org

Ms. Faye Lau / Ms. Manda Wong 刘美儿小姐 / 黄敏华小姐 电话Tel: (852) 2155 5123 电邮Email: faye.lau@hkpcashow.org /

Ms. Ellen Jin / Ms. Amanda Li 靳红红小姐 / 李明宇小姐 电话Tel: (86) 181 2405 6937 / (86755) 8624 0033 电邮Email: ellen.jin@hkpcashow.c

电邮Email: ellen.jin@hkpcashow.org / amandali@hkpca.org

#### 承办单位

柏堡活动策划 Baobab Tree Event Management Co., Ltd.

Ms. Carmen Feng / Ms. Jenny Zeng / Ms. Kelly Lo 冯家敏小姐 / 曾翠珍小姐 / 卢霭汶小姐 电话Tel: (86) 133 6057 8272 / (86) 132 0263 9367 / (86) 134 3411 6069 / (852) 3520 3612

电邮Email: info@hkpcashow.org QQ: 2387451739

HKPCA

HKPCA

HKPCA SHOW HKPCA SHOW HKPCA

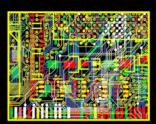

### **Routing Strategies** to Minimize Radiation

#### **Beyond Design**

by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

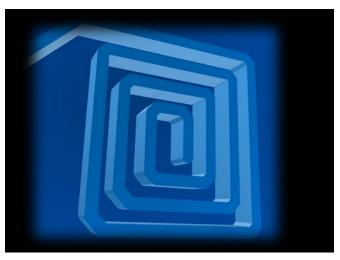

Electromagnetic (EM) energy propagates through the dielectric materials of a multilayer PCB guided by the signal traces between the planes, for inner stripline layers (Figure 1), but it acts slightly differently on the outer microstrip layers. Microstrip layers generally have a solid ground reference plane on one side but allow radiation from the boundless surface into the air. A well-thought-out routing strategy can avoid up to 10 dB of radiation from the substrate. Embedding signals between the planes reduces these emissions, and susceptibility to radiation, as well as providing electrostatic discharge protection. So, not only can

Microstrip **GND Plane** Stripline **PWR Plane**

Figure 1: Microstrip EM fields (top) and stripline EM fields (bottom).

one prevent noise from being radiated but also reduce the possibility of being affected by an external source.

Studies conducted by Hewlett-Packard have found that there are up to 20 dB greater emissions from edge-located traces compared to traces located in the centre of the board on outer layers. Yet the same test performed on buried traces indicated no change as the traces were placed nearer the PCB edges. This implies that it is best to keep well away from the edge of the board when routing on the outer microstrip layers. The impedance changes as the reference plane decreases in the area beneath the trace.

On a multilayer PCB, critical signals should be routed on a stripline layer adjacent to a solid reference plane to reduce radiation. The spacing between the signal trace and the return plane should be as small as possible to increase coupling and reduce the loop area.

The three constraints to keep in mind:

- Keep the mark-to-space ratio of the waveform equal as this eliminates all the even harmonics.

- Route high-speed signals between the planes, fanout out close to the driver (200 mils) dropping to an inner layer, and route back up to the load again with a short fanout.

- Use the same reference plane (GND if possible) for the return signal, as this reduces the loop area and hence radiation.

# PR(0) // [S

AMERICAN MANUFACTURING INGENUITY AND STRENGTH

#### Houston

Meticulously prints the legends on circuit boards that identify vital information.

#### Steven

Maximizes production panel assembly yields with precise routing and scoring.

#### Natasha

Carefully applies solder mask coatings using direct image machines.

#### **Aaron**

Assembles and laminates layers of circuitry into multilayer PCBs.

#### Charles

Carefully applies solder mask coatings using direct image machines.

Rigorously tests every electrical circuit path.

AMERICA'S ONLY HUBZONE PCB MANUFACTURER

| Signal<br>Layer<br>Number | Layer<br>Inductance<br>(nH/m) | Layer<br>Capacitance<br>(pF/m) | Layer<br>Propagation<br>Velocity (m/s) | Trace<br>Length<br>(inches) | Trace<br>Inductance<br>(nH) | Trace<br>Capacitance<br>(pF) | Flight<br>Time<br>(ps) |

|---------------------------|-------------------------------|--------------------------------|----------------------------------------|-----------------------------|-----------------------------|------------------------------|------------------------|

| 1                         | 311                           | 110                            | 1.71e+8                                | 2.0000                      | 15.80                       | 5.59                         | 297.08                 |

| 4                         | 354                           | 112                            | 1.59e+8                                | 2.0000                      | 17.98                       | 5.69                         | 319.50                 |

| 6                         | 356                           | 148                            | 1.45e+8                                | 2.0000                      | 18.08                       | 7.52                         | 350.34                 |

| 7                         | 356                           | 148                            | 1.45e+8                                | 2.0000                      | 18.08                       | 7.52                         | 350.34                 |

| 9                         | 354                           | 112                            | 1.59e+8                                | 2.0000                      | 17.98                       | 5.69                         | 319.50                 |

| 12                        | 311                           | 110                            | 1.71e+8                                | 2.0000                      | 15.80                       | 5.59                         | 297.08                 |

|                           |                               |                                | Total                                  | 12.0000                     | 103.72                      | 37.60                        | 1933.84                |

|                           |                               |                                |                                        |                             |                             |                              |                        |

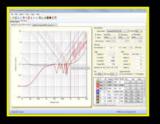

Figure 2: Relative signal propagation of microstrip and stripline (simulated in iCD Design Integrity).

The electric fields surrounding the microstrip exist partially within the dielectric material(s) and partially within the surrounding air. Since air has a dielectric constant (Dk) of one, it will speed up the signal propagation compared to the stripline. Even if the trace widths are adjusted on each layer, so as the impedance is identical, the propagation speed of microstrip is always faster than stripline-typically by 13-17%. The speed of propagation of digital signals is independent of trace geometry and impedance.

If you are aware of this issue, then the flight time (as shown in Figure 2) can be matched to compensate for the varying trace delays, so that at the nominal temperature, all signals running on either microstrip or stripline will arrive at the receiver simultaneously. Alternatively, many routers these days have matched delay routing which enables one to take the flight time variation between microstrip and stripline configurations into account. Note that matched delay is quite different from matched length routing which does not consider flight time.

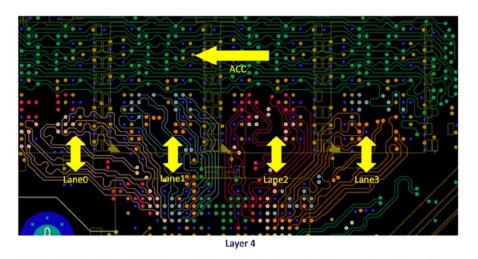

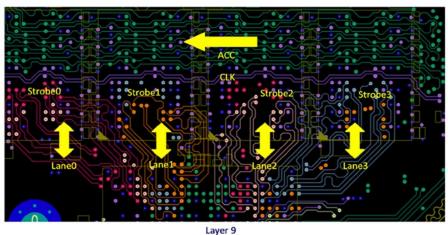

For the DDR3/4 fly-by configuration, for instance, it is best to route all the critical traces on two symmetrical paired layers. In this case, the paired layers are 1 and 12, 4 and 9, plus 6 and 7. Layers 4 and 9 are best, as they are embedded and close to the plane pairs and active devices of a 12-layer PCB. There are 200mil fanouts from the microstrip layer to these (not shown). These two layers have identical delays of 319.50 ps and are symmetrical in the stackup embedded between planes. Figure 3 shows the routing directions of the data lanes (0-3) combined with the associated differential strobes and the address, control and command (ACC) signals combined with the differential clock. One does not need to worry about layerinduced flight time skew because layers 4 and 9 are identical.

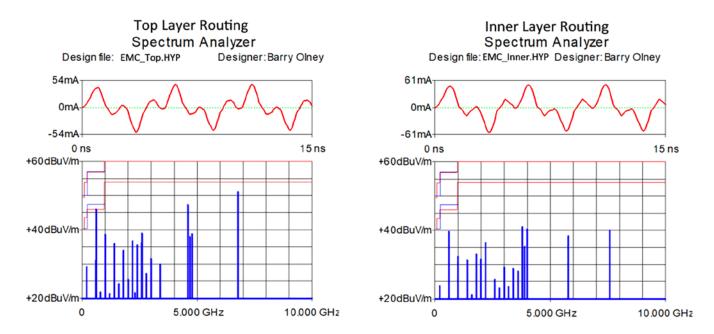

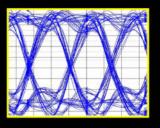

Figure 4 graphs the relative radiation between outer and inner layers. In this case, the trace routed on the inner layer 4 exhibits between 4 to 10 dB less noise than the trace routed on the top layer. Note that there are radiating harmonics above 40 dB on the top layer routing. Also, high frequency components radiate more

Figure 3: Routing strategy for DDR3 fly-by configuration.

readily because their shorter wavelengths are comparable to trace lengths, which act as antennas. Consequently, although the amplitude of the harmonic frequency components decreases, as the frequency increases, the radiated frequency varies depending on the trace characteristics.

So, apart from the short 200mil microstrip fanouts, the emissions of this design are well below that of the FCC/ CISPR Class B limit (lower red line). Whereas, the radiation would have been 49.73 dB at 6.76 GHz and 52.10 at 7.8 GHz if it was routed on the outer layers, possibly failing testing. If you plan your routing strategy and stackup design prior to commencing the layout, then design for electromagnetic compliance takes very little extra effort.

Figure 4: Comparison of radiation from signals routed on the top microstrip layer vs. inner stripline layer.

#### **Key Points**

- Embedding signals between the planes reduces these emissions and susceptibility to radiation as well as providing electrostatic discharge protection.

- It is best to keep well away from the edge of the board when routing on the outer microstrip layers.

- On a multilayer PCB, critical signals should be routed on a stripline layer adjacent to a solid reference plane to reduce radiation.

- The propagation speed of microstrip is always faster than stripline—typically by 13-17%.

- Many routers these days have matched delay routing which enables one to take the flight time variation into account.

• The trace routed on the inner layer 4 exhibits between 4 to 10 dB less noise than the trace routed on the top layer. DESIGNO07

#### Resources

1. Beyond Design by Barry Olney: The Fundamental Rules of High-Speed PCB Design Part 4; Embedded Signal Routing; Signal Flight Time Variance in Multilayer PCBs.

Barry Olney is managing director of In-Circuit Design Pty Ltd (iCD), Australia, a PCB design service bureau that specializes in board-level simulation. The company developed the iCD Design Integrity software

incorporating the iCD Stackup, PDN, and CPW Planner. The software can be downloaded at www.icd.com.au. To read past columns, click here.

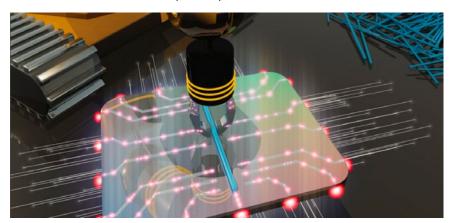

#### Discovery of New Nanonwire Assembly Process Could Enable More Powerful Computer Chips

In a newly-published study, a team of researchers in Oxford University's Department of Materials led by Harish Bhaskaran, Professor of Applied Nanomaterials, describe a breakthrough approach to pick up single nanowires from the growth substrate and place them on virtually any platform with submicron accuracy.

This technique is readily scalable to larger areas, and brings the promise of nanowires to devices made on any substrate and using any process. This is what makes this technique so powerful.

The innovative method uses novel tools, including ultra-thin filaments of polyethylene terephthalate (PET) with tapered nanoscale tips that are used to pick up individual nanowires. At this fine scale, adhesive van der Waals forces (tiny forces of attraction that occur between atoms and molecules) cause the nanowires to "jump" into contact with the tips. The nanowires are then transferred to a transparent dome-shaped elastic stamp mounted on a glass slide. This stamp is then turned upside down and aligned with the device chip, with the

> nanowire then printed gently onto the surface.

Deposited nanowires showed strong adhesive qualities, remaining in place even when the device was immersed in liquid. The research team were also able to place nanowires on fragile substrates, such as ultra-thin 50 nanometre membranes, demonstrating the delicacy and versatility of the stamping technique.

(Source: University of Oxford)

Jan. 21-26

FERENCE Jan. 24-26

SAN DIEGO CONVENTION CENTER | CA

### ADVANCE IN A NEW ERA

technology

cyber security

automation

packaging

data analytics

**Factory of the Future**

networking

substrates

innovation

transformation

Advance your career in a new era of electronics manufacturing with networking at IPC APEX EXPO 2023. Meet leading innovators and designers, connect with peers, and create new business opportunities at North America's largest gathering of electronics manufacturing professionals on our world class show floor.

IPCAPEXEXPO.ORG

#IPCAPEXEXPO

MEET AND GREET AT OUR SOCIAL RECEPTIONS INCLUDING THE NEW CAREER **CONNECTIONS NETWORKING EVENT WEDNESDAY, JANUARY 25!**

### The Learning Curve for Ultra HDI

#### Feature Q&A With Tara Dunn

For this issue on ultra HDI, we reached out to Tara Dunn at Averatek with some specific questions about how she defines UDHI, more about the company's patented semi-additive process, and what really sets ultra HDI apart from everything else. Do designers want to learn a new technology? What about fabricators? We hope this interview answers some of those questions that you may be having about these capabilities and what it could mean for your designs.

**Q:** How do you define ultra HDI? What is the cutoff in mils or microns?

A: That is an excellent question. At this point I think it means different things to different people depending on where their current "HDI" capabilities are. IPC has created an ultra-HDI working group and I believe the definition they are working with is that to be considered ultra-HDI, a design needs to include one or more of these parameters: Line width below 50 µm, spacing below 50 µm, dielectric thickness below 50 µm, and microvia diameter below 75 µm.

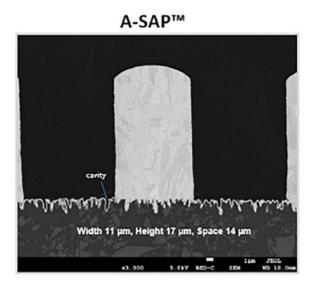

**Q:** Averatek has developed the A-SAP<sup>™</sup> semiadditive process, which can produce traces down into the UHDI space. Can you clear up the differences between mSAP and A-SAP, and what this means to designers and design engineers?

A: In general, SAP, or a semi-additive process, is a process that starts with a very thin layer of copper and then builds the trace patterns from there. One common differentiating factor in these two approaches to SAP is the starting copper thickness. Typically, copper thickness that is 1.5 microns or above would be considered mSAP, or a modified semi-additive process. Because the copper is a little thicker than other SAP processes, it requires more etching, which can have impacts on trace width and space and also the sidewalls of the trace. This

### We Find Solutions To Your Design Needs

#### **APCT Is The Solution**

- Technological Innovation

- Detailed Engineering Support

- Consistently Reliable Quality

- Exceptional Cycle Times

- Knowledgeable Technicians

- Trustworthy Personnel

Printed Circuit Board Solutions

APCT.com

APCT Santa Clara HQ 408.727.6442

**APCT Anaheim** 714.921.0860

APCT Orange County 714.993.0270 APCT Wallingford

APCT Global

203.269.3311

203.284.1215

process can typically provide features as small as 30 microns in highly specialized facilities that are running extremely high-volume manufacturing. This technology is commonly seen in our smartphones.

Averatek's A-SAP begins with a much thinner electroless copper, typically 0.2 micron and this copper thickness, or thinness if you will, enables the fabricator to produce much finer feature sizes. The technology is capable of traces and spaces as small as 1 micron if the fabricator has advanced imaging equipment. Typically, PCB fabricators have equipment that can image traces to 12.5 µm today. There are also signal integrity benefits to this process. Because the base copper is so thin, there is minimal impact on the trace sidewalls, and greater control to line width resulting in impedance control tolerance improvements.

One other difference between the mSAP and A-SAP technologies is in the ratio of trace height to trace width. mSAP processes allow a 1:1 ratio of height to width and A-SAP traces can be produced with aspect ratio of 2:1 or greater. For example, a 25-micron wide trace could be 40 microns tall. This has gotten a lot of attention from a signal integrity perspective.

**Q:** How is designing in the ultra-HDI arena different from designing a typical PCB, or even an HDI board?

**A:** I sometimes worry that designers will think they must learn a whole new way to design if they want to work with ultra HDI designs. I believe it is not that different than when a designer first learns to design with flex materials. Most things are the same as designing with rigid and once you learn the specific items that are different and why, designing with a new technology becomes much easier.

That said, this does give the industry the opportunity to reimagine how PCB design is done. In general, the constraints have been at 75-micron line and space for so long that, collectively, we have learned to work around that with blind and buried vias, stacked and staggered microvias, an increasing number of lamination cycles to create enough space to route out tight pitch BGAs, etc. The SAP processes and finer line widths can free up valuable real estate and help to simplify the design and reset the technology curve.

There are a couple of different ways to approach a design with ultra HDI and I think the approach varies according to a designer's particular priorities. For some, the priority is overall miniaturization, which may be in size, or overall thickness. For others, a top priority is via reliability and the focus is on reducing lamination cycles or even using space to increase hole size and move from an HDI construction to a through-via construction.

Circling back to the flex comparison, I want to be sure to mention that SAP processes can be built with a variety of materials including flexible materials and that not all layers in a PCB design need to be done with SAP. It is a layer-by-layer selection, and it is common that power and ground layers, or any layer with only 75 micron or greater feature sizes will be built with subtractive etch process.

What are some of the benefits of UHDI?

**A:** I think the primary benefits are:

- Dramatic size and weight reduction over current subtractive etch processing. PCBs can be made much smaller and thinner.

- **Improved reliability:** This could be f rom reduced layer count, reduced lamination cycles, reduced dependence on microvias, etc.

- Improved signal integrity: As I mentioned, higher aspect ratio of height to width, which opens up several things to PCB designers, and tighter control on feature sizes improves impedance control.

- Reduced costs: This one may seem coun-

terintuitive, but it is rare that costs are compared as apples to apples. I often see designs reduce layer count, reduce laminations, and shrink overall size. All these things simplify the design, improve yield, and reduce costs.

• Biocompatibility: I don't think I mentioned earlier, but the A-SAP process begins by completely removing the copper foil and a thin layer of electroless copper is added to the dielectric. But this process is not limited to only copper. I have seen several applications where gold and platinum are used as the conductive metal. This, done with polyimide or LCP, provides a much more biocompatible solution for medical applications.

**Q:** What are some of the hurdles facing designers-and fabricators-who work on UHDI boards?

A: In my mind, the biggest hurdle is the learning curve that both designers and fabricators need to go through. Fabricators are learning a new process, and while that process of creating the traces is not difficult, it does need to mesh with other processes. For example, what is the new process for via-in-pad-plated over or what thickness of copper can be plated in the hole? There may be different approaches based on customer design. Fabricators are well-versed in using various techniques to meet customer needs and this is no different, but it does require thought and experience.

From a design perspective, as we mentioned earlier, there are a lot of questions. How do you design with controlled impedance at these fine lines? There are white papers, by the way, to help with that. What materials are compatible with this process? Where does it make sense to use subtractive etch vs. SAP layers? Is there reliability data? These are a few of the common initial questions.

**Q**: Are there any resources—books, websites, instructors, etc.-for UHDI design techniques? I imagine people are coming to Averatek with questions.

A: Yes, we do field a number of questions, which is one of the best parts of my role at Averatek, and along with the work we are doing, we are also working with a number of PCB designers who are interested in really understanding how to apply these fine features. These designers are starting education programs, writing papers, presenting at conferences, and are available to assist as others go through this learning curve.

A good place to start is the Info Center on Averatek's website, where we have compiled a number of white papers and articles addressing the subject. I also believe most of the PCBfocused trade shows are now offering tracks about SAP and I have seen several webinars available as well, both from fabricators and from equipment suppliers such as Orbotech.

**Q:** What advice would you give designers who are considering moving into UHDI?

A: It is the same advice I give to anyone new to designing with HDI, new to designing with flex or rigid-flex, and now new to designing with ultra HDI: Work closely with your fabricator. Learn to understand their capabilities and let them help guide you through the design. They have the experience of building many designs with these technologies and are always happy to help PCB designers design a manufacturable part. DESIGNOO7

Tara Dunn is the vice president of marketing and business development for Averatek and an I-Connect007 columnist. To read past columns, click here.

### The ABCs of **Clean Schematics**

#### **Connect the Dots**

by Matt Stevenson, SUNSTONE CIRCUITS

The production team is always excited when the first shipment of boards for a new electronic device comes back from the PCB manufacturer. Anticipation builds as the engineer connects the first set of components, puts everything together, and gets ready for that first test.

But when something goes wrong—a tiny pop, a sizzle, a puff of smoke, or nothing happens at all—the mood can turn from excitement to frustration. The engineer performs a postmortem and discovers a pinhole melted into the integrated circuit (IC), and then the culprit (a missing decoupling capacitor) led to a completely predictable voltage spike.

Where did the process go wrong? The engineer is certain that they put the capacitor in the right place. However, on closer examination, perhaps it is not close enough to the IC pad. Is it the fault of the PCB designer? Chances are that the designer will claim that they put the capacitor right where the schematic said it should be.

In a case like this, the fix is easy. The designer and the engineer get on the same page and produce a new design in 15 minutes. Unfortunately, the current batch of boards is now only useful as a set of coasters—delaying the project and potentially creating budget overruns.

This is a common issue for electronics manu-

facturers, and it is completely avoidable.

When engineers start to put together projects, the schematics are vital to good communication with the PCB designer. Theirs is a team effort. The schematic is where the engineer thinks through the project. However, by the time they hand it off to the designer, it needs to be a clean, comprehensible document that isn't vague and doesn't confuse. Most importantly, the engineer needs to communicate everything the PCB designer needs to design the right board for the project.

# Solutions for All Aspects of RF/Microwave Design

#### **Access Premiere RF Analysis with AWR**

Dramatically reduce development time and cost for components, circuits, systems, and subsystems employed in wireless, high-speed wired, broadband, aerospace defense, and electro-optical applications with the highly-integrated AWR Design Environment. From amplifiers, antennas, and communications to filters, passives, and radar, the comprehensive AWR platform provides everything needed to solve your toughest design challenges.

Get The FREE Trial >>>

cādence°

#### **Best Practices Are There for a Reason**

We all know that best practices exist, but real-world circumstances often lead to cutting corners. Saving time by ignoring best practices—like performing one last design check before submitting to the manufacturer—is just going to cost more time and money later. Even though it seems exhausting and repetitive, best practices involve starting at high-altitude block diagrams and then breaking each block into schematic sheets, checking flow and accuracy carefully, and then finally designing the board.

After that, a best practice has the engineer and designer picking over the design carefully, ensuring that it matches the specs-before it goes to the PCB manufacturer.

#### **Designers Will Do What You Tell Them to Do**

Engineers need to remember that designers don't read minds; they read schematics. The engineer may understand implicitly the locations for all their bypass capacitors, but they can't rely on the designer's interpretation to properly place the elements. Instead, locate devices in roughly the manner of the final design to help the designer avoid bad interconnects, placement assumptions, or other errors.

It never hurts to provide the designer with explanatory notes about the elements. You will never hear a designer say that the engineer provided too much guidance for their work.

For example, utilize good naming conventions for connections or net names. Automated labels from design software are rarely helpful or intuitive. Create labels a human can understand.

#### Leverage Your Tools, But Don't Use Them as a Crutch

Sometimes, engineers will give implicit connections using port symbols for the entire schematic. Unfortunately, this practice leaves no trail for the designer to follow. While the engineer may have saved a couple of minutes, the designer spends more time sorting out the nest of connections.

Let the software be on your side. It tracks and confirms those connections for a reason. This may feel like an obstacle for the engineer, but for the overall project, these tools are a lifeline.

The design rule check (DRC) is another example where the tool exists, but results may get ignored in the interest of saving some time. Too often, issues are ignored because they seem unimportant. However, over time these errors build up and create a confusing mess that may obscure errors that are truly important. One of your team's best practices should be generating a DRC report that reads no warnings and no violations.

#### More Recommendations for **Clean Schematics**

In addition to the broader best practices of fostering good communication and not relying too much on technology, the following are key methods that help ensure a clean schematic and a manufacturable, functional PCB design.

- Design the schematic in the design program and label all connects with comprehensible net names—no auto-generated names

- Lay out the schematic in a manner that clarifies locations

- Label the schematic so that the next person can understand it

- Create an environment where designers are comfortable asking for clarification if they are uncertain how to proceed

- Use the DRC and address the warnings and violations it reports

Well-designed schematics will save time, money, and frustration both for your current project and future endeavors. If your schematic is nice to look at and easy to understand, your team can utilize blocks for other similar projects down the road. Teams that commit to good schematic practices win the long game.

#### **Commit to Best Practices** and Good Process

We all want to create great final products. Designers want to make great boards. Engineers want to make great schematics. To get there, we also need to think about making the work of the next person easier. When you commit to best practices, clear communication, and clean schematics, everyone benefits. DESIGNOO7

Matt Stevenson is the VP of sales and marketing at Sunstone Circuits. To read past columns or contact Stevenson, click here.

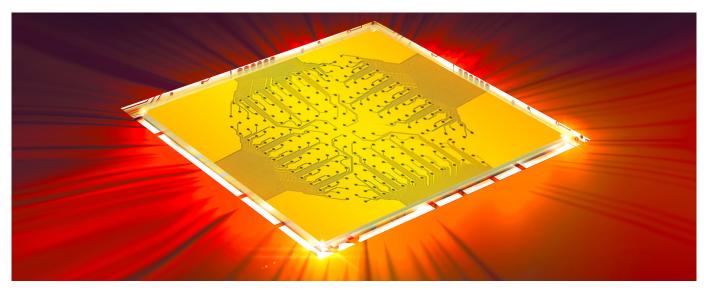

#### A World First: Self-calibrated **Photonic IC:**

#### New Interchange for **Optical Data Superhighways**

Research led by Monash and RMIT Universities in Melbourne has found a way to create an advanced photonic integrated circuit that builds bridges between data superhighways, revolutionising the connectivity of current optical chips and replacing bulky 3D-optics with a wafer-thin slice of silicon.

This development, published in the prestigious journal Nature Photonics, has the ability to warpspeed the global advancement of artificial intelligence and offers significant real-world applications such as:

- Safer driverless cars capable of instantly interpreting their surroundings

- · Enabling AI to more rapidly diagnose medical conditions

- Making natural language processing even faster for apps such as Google Homes, Alexa and Siri.

- Smaller switches for reconfiguring optical networks that carry our internet to get data where it's needed faster

Whether it's turning on a TV or keeping a satellite on course, photonics (the science of light) is transforming the way we live. The photonic chips can transform the processing capability of bulky bench sized utilities onto fingernail sized chips.

The project's lead investigator says this breakthrough complements the previous discovery of Monash University's Dr. Bill Corcoran who, in partnership with RMIT in 2020, developed a new optical microcomb chip that can squeeze three times the traffic of the entire NBN through a single optical fibre, regarded as the world's fastest internet speed from a single fingernail-sized chip.

The optical microcomb chip built multiple lanes of the superhighway, now the self-calibrating chip has created the on and off ramps and bridges that connect them all and allow greater movement of data.

(Source: Monash University)

# MilAero007 Highlights

#### Will Marsh: CHIPS Act Update >

Nolan Johnson reconnects with PCBAA President Will Marsh, who brings him up to speed on the initial stages of implementation and administration, and provides more insight on the Supporting American Printed Circuit Boards Act of 2022.

#### A Deeper Look at the CHIPS Act Investment >

In this interview with Chris Peters at U.S. Partnership for Assured Electronics (USPAE), Nolan Johnson seeks for better understanding regarding the implications of funding the CHIPS Act. Frankly, where and how will the \$52 billion be spent? Who will decide how the funds are allocated?

#### **North American PCB Industry Sales Up 15.1% in August >**

IPC announced the August 2022 findings from its North American Printed Circuit Board (PCB) Statistical Program. The book-to-bill ratio stands at 0.98.

#### **IPC APEX EXPO 2023 Offers New Courses, New Instructors,** and IPC E-Textiles

Registration is now open for IPC APEX EXPO 2023, to be held at the San Diego Convention Center in San Diego, Calif., Jan. 21–26, 2023.

#### **Boeing Invests \$5M in Advanced** Manufacturing Innovation Center >

Boeing announced it is investing \$5 million to help expand the Advanced Manufacturing Innovation Center in St. Louis. The invest-

ment will help fund a state-of-the-art advanced manufacturing facility and grow the region's talent pipeline and technical and manufacturing abilities.

#### **Electronics Industry Calls for U.S. Presidential Determination** on Key Components Under **Defense Production Act**

The electronics industry is calling on U.S. President Joe Biden to address urgent industrial base vulnerabilities and deliver on the promise of the CHIPS Act by prioritizing domestic development of printed circuit boards and integrated circuit substrates under Title III of the Defense Production Act.

#### **Designing Through Supply Chain Pain**

Engineers are accustomed to the demanding challenges of designing for miniaturization, cost reduction, cross platform compatibility, and harsh environments. What has proven to be the most painful experience of my career (and for many of my colleagues) is the sheer lack of components from which to build our designs.

#### **CAES Wins Contracts for Development** of Next-Generation, Octa-Core, User-Selectable CPU for Space >

CAES, a leader in advanced mission-critical electronics for aerospace and defence, announced that it has won multiple contracts with the European Space Agency (ESA) for the development of the GR765 Systemon-Chip (SOC), the first user selectable CPU for space.

# Ultra High Density Circuit Board Design

#### **Designers Notebook**

Feature Column by Vern Solberg, CONSULTANT

To facilitate new generations of high I/O semiconductor packaging, circuit board technology is undergoing significant refinement in both fabrication process methods and base materials selected. Many of the new high-function semiconductor package families require significantly more terminals than their predecessors. Interconnecting these very finepitch, high I/O semiconductors can dramatically affect the procedures used in both circuit board design and assembly processing.

When defining the complexity level for the HDI circuit, the designer will first establish a criterion for fabricating the circuit board. This will include the board outline, thickness limitation, and any special features required for the end product. A clear objective will be established to identify the maximum number of circuit layers that are to be dedicated to signal routing and the number of layers reserved for power and ground distribution. Establishing the required number of signal layers will be determined by the overall component density and interconnect complexity.

#### **Interconnect Capacity Analysis**